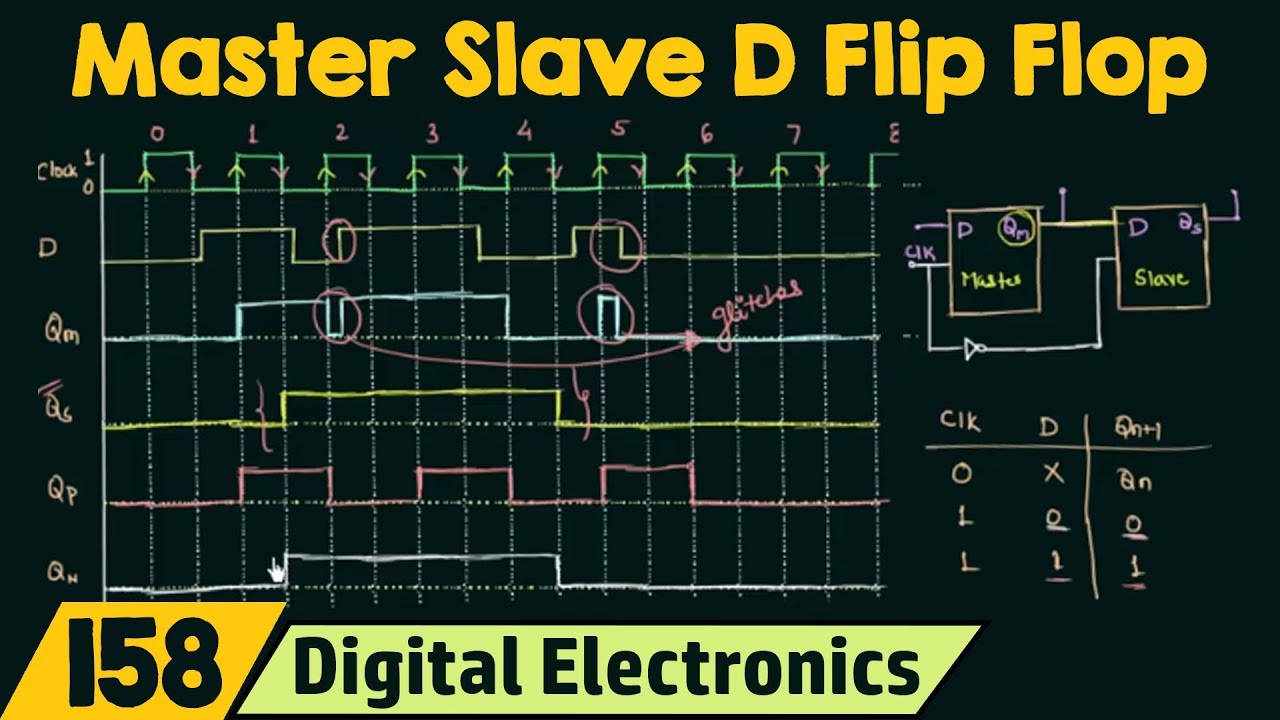

Digital Electronics: Behavior of Master Slave D Flip Flop

Digital Electronics: Behavior of Master Slave D Flip Flop

Contribute: http://www.nesoacademy.org/donate

Website ► http://www.nesoacademy.org/

Facebook ► https://goo.gl/Nt0PmB

Twitter ► https://twitter.com/nesoacademy

Pinterest ► http://www.pinterest.com/nesoacademy/

Best comment

- shubhang kulkarni: why isn't a glitch observed in Qs?

- samar nabil: thanks alotttttt

- Ashim Singh: Question : Why is the output high / low till the next level or edge ?

- Lajos György Mészáros: If I invert the clock by default, will the master-slave flip flop turn into a positive edge triggered flip flop?

- Raja Haseeb: +Neso Academy sir as you say we use master-slave or -ve Edge triggered to remove glitches but here sir if we see the output of +ve Edge triggering they are also free from glitches same in case jk ff we can also avoid racing using +ve edge triggering am i right sir ????? correct me if i am wrong

- arghya dhar: It seems like the master d flip flop is level as well as edge sensitive ! Is that even possible?

- Indu reddy: For d flipflop the o/p and i/p are same

- Roshan pandit: Sir how to learn verilog Language in vlsi design

- Tech lover: Chalti kya randi

- Utkarsh ahuja: Sir which software do you use for making these lectures and on which desktop/pad ?

- Harish Kanna: Couldn't understand when and why the signal goes up or low..Pls someone give me crct explanation

- Panidhra Kumar: how D wave generated

- M Q: Because the input signals are only changed when the clock is at the high edge for the Qp (positive triggered flip-flop).

- 80sROCKKKKK: Yeah... hopefully the help didn't come too late. Or that it didn't matter :)

- HANBO: +Kirsteen Ng yes, if it is constructed with NAND it's positive(rising) edge triggered, otherwise NOR negative(falling) edge triggered

- Gunjan Jaiswal: what are data lock out flip flops?

- Abhimanyu Yadav: are Qm and Qs trigerred by level trigerring and Qp and Qn by edge trigerring?????????

- diivya k.s: :)

- MUHAMMED YASEEN C ee14b096: 1. To overcome glitch 2. To get negative edge triggered D flipflop using level-triggered clock

- Jake Young: Wait so a Master Slave D flip flop is the same as a negative (or falling edge) D flip flop???

- all in one: the difference between my class teacher and you is...i feel sleepy and headache when my teacher giving lecture..but i feel fresh happy and wish to see your whole lecture continue....love you alot sir...thank you so much for all your did..

- Sagnik Basu: why is the d flip flop acting as level sensitive device?? Please explain..

- 80sROCKKKKK: He made a mistake. D changes only at the positive edge... he assumed erroneously that it changes while the clock level is 1. That too only some times. It's okay, humans make mistakes

- Mohammad Azhar: well it's always informative. it's really helpful.

- Kirk Hammer 2010: I know the content is invaluable , But How about i pay 10 Rs tribute for each of your video (dont judge me) Contribute: http://www.nesoacademy.org/donate

- Phy Enthusiast: this is gold

- Anastacio Monsivais: Thank you so much. The video is explained clearly with details

- Lavi ben-shimol: I learned that dff reacts to clock changing (and just that clock moment when it goes up) and there is latch dff which passing d to q as long as he have logical 1 in the clk in this video, it seems you working with latch dff i think you should write it in description because it might confuse people besides that. awsome video and awsome explain you really helping! thank you.

- hang man: why in drawing Qs we do not consider inverse of the clock ?? anyways gr8 video (y)

- Sahil Arora: there is no glitch in Qp

- kirti kansal: fantabulous...mind blowing lecture..

- rishabh thakur: Sir, thank you for the wonderful video.i have a doubt,what is structure of postive and negative edge triggered d flip flop?

- AMAN KUMAR: Simplest and best explanation, hats off man!!

- sofie Chrash: wich one is now the improtant output?

- Utkarsh ahuja: Sir which software do you use for making these lectures and on which desktop/pad ?

- somethingNEW: please be point to point slowly...

- Mohit Gouniyal: Sir, please provide these lectures in a order.initially they are in order but as I go further in the presentations their order is random.

- Vaishnavi Ganseh: Outstanding video. Thank you very much!

- mutum arnica: Why is master slave used in d flop flip ?why not just use d flip flop

- Neso Academy: If you've followed the earlier lectures then it should not be a problem.

- Cyber Snow: Great video and explanation :D

- David Pham: Outstanding video. Thank you very much!

- Cyber Snow: Qpositive Qnegative edge triggered

- ASHOK DASARI: what is qp and qn

- Mohit Gouniyal: thank you

- Cherukumudi Saisrividhya: If there is a word more than a perfect it deserves u a lot. Such a clarity and patience I wonder really how u developed!!!! Seriously speechless sir.... We r really blessed by God. Thanks.keep rocking all d best sir. Hope all ur dreams come true in the upcoming future

- Nithya G: Thank you very much

- master chef: why is the master part of the d flip flop level sensitive?? It is the same as a d flip flop.!..Please help me

- Saniya Farahath: That was brilliant. I love you!

- Bee A: I didn't understand very well :( in some times you look at the diff. between the lines, and some times you just ignore

- Pratima Singh: very nice :)

- RAKESH REDDY THEEGHALA: and also the 121 lecture is missing

- Gerenzoo: Qm is level-triggered, while Qp is the output of a positive edge triggered D-FlipFlop

- Sahil Singh: this one is marvelous.

- Ayah Ahmad: what if it has time delays? how will it be drawn

- HANBO: Hello Sir, when u do the timing waveform, can u please also introduce some timing parameters, such as setup time, hold time and propagation delay? My textbook mentioned this a bit, but I would like to know more details about this, thank you!

- La Premiere asd: Excellent video, thank you so much

- Salil Singh: what is the point of having a master slave config for d flip flop. as in master slave solves the 1-1 condition in j-k flip flop....we dont have a 1-1 state in d flip flop.

- Chandra Shekhar Agrawal: Sir, how can we draw truth table for J-K master slave flip flop?

- ibrahim mehmood: please tell me that why is Qp and Qm not same?

- Level2 Term1: Is "Negative Edge Triggered Flip Flop" an abstract idea (which can be achieved by a master-slave flip flop)?

- RAJENDRA KUJUR: I didn't get the positive and negative edge triggered

- pratik solanki: is it true that if we use edge triggering we will not have glitches? Ans plz......

- diivya k.s: Better late than never!

- prerna bhalla: You make things so simple to understand :D

- Nilotpal Mishra: no words, each and every word is important ....flow of explanation is mind blowing

- K X: agree, what I learned is also showing that the change only happens when the clock changes from 0 to 1.

- Ronak Kumar: Be a liitle bit slow. The pace is good in the beginning slides but it changes at the end. Slides are absolutely fantastic

- Muhammad Jasrul Haikal: Brilliant sir. Thanks

- Ch akm: you make me so happy .thanks again you are realy a good teacher .

- Usman Shah: Superb methodology sir keep it up. Thanks

- Fandus Mercius: thats all i think

- Niharika Niha: Can anyone plz explain why sir didnot considered the glitches in slave flip flop

- RAKESH REDDY THEEGHALA: I don't understand what is triggering

- Srineesh Salur: thank you👌😳😳😘😘😘

- Utkarsh Sharma: your expaination is very much better than class lectures. really outstanding...

- VST GUY: there s no truth table sir!

- shubhang kulkarni: when Qm catches a glitch even Qs should catch a glitch.but why doesn't it catch a glitch?

- Yash Raj: Ariel Góes de Castro A Latch uses enable(not a clock) while Flip-Flop uses clock.

- Emre Arslan: Sir could you be an angel sending from heaven to save me ? <3<3

- Nisarga Yadhu: U deserve more subscribers. Very informative video : )

- vaibhav pancholi: sorry sir but i am not able to understand that how you are ploting the graph....

- Surendra Parla: but master is also a positive triggered flipflop

- MB Design: Very good! I m currently looking for a timing diagram for a positive edge triggered master/slave D flip flop. I m curious about the storage process in a diagram. Has anyone a tip?

- Lalatendu Pati: Throughout my semester I have seen your videos and it is very very helpful.... I will request you to make a lecture series on Analog Communication Technique... Thank you very much...

- Vignesh Kamath: What happens if input signal changes when clock is low do we have glitches in slave flip flop?

- venkataramana venkataramana: when you analysis the ff for the output of Qm and Qs it act as alevel sesitive, becz as there is a change in d-ff input the output changed. But when you do analysis on by considering individual ff you consider the edge triggering.. whyy??? please explain..............................

- Apostolos Mavropoulos: Hello sir! does master slave flip flop only works on level triggering or both?

- Sourav Raj: where is Qp and Qn in diagram

- titus varughese: Master is a D-latch and slave is also a D-latch but when you combine both the Master D-latch with the slave D-latch it produces a negative triggered flip flop, ( i think, its because of the inverter from the clock signal that connects to slave latch) as shown in the video. hope this helps

- Joshua Dyer: Liked, subscribed, and shared with friends. Beautifully demonstrated and summarized. You are a wonderful asset to students!

- Surendra Parla: see master is actually a d flipflop and result obtained from it Qm and Qp is also a d flipflop .but why Qm has glitches and Qp doesnt. Infact Qm shouldnt have glitches as it is a D flipflop

- HIMANSHU SINGH: may be to avoid glitches though we can use (-)ve edge trigger d flip flop in place of MS d flip flop

- RuhiTaj: In Qm, for 2 clock cycle, the Qm should not raise right?? Because, the D flipflop is a edge triggered one, It changes, only during the edge raising and continues till the end of the clock cycle. Please correct me, if Iam wrong! Thank you for your awesome videos.

- Henrique Baqueiro: I know the behaviour, what I wanted to know is how to build flip flops with logic gates...

- Ariel Góes de Castro: so it isn't a flip-flop, it's a latch, correct?

- Mohamed Khalil: Hello what happens if we used slave Flip Flop only , what will be the truth table of it?

- diivya k.s: Thanks:)

- mutum arnica: Why is master slave used when there is no race around condition in d flip flop

- Lsf Lastborn: Very straightforward and well explained.... Gracias

- Kirsteen Ng: Great video! One question though, is there any other way we can tell it is a falling edge triggered flip flop without drawing the time graphs? Thanks!!!

- Neso Academy: +hang man I have considered the inverse of the clock. Because of NOT gate, slave ff will be operational for the low clock pulse. This means when clock is low actually its high for slave ff. If you wan't to show a separate inverted clock you can but its good to consider that slave ff is operational for low pulse with same clock. Because system has only one clock given simultaneously to all the processes. And drawing complimented clock separately will lead to confusion. Thank you!

- Sachin singh: sir what are 'Qp' and 'Qn'

- Monika Sharma: Does glitches occur only in d flip flop

- shubham sinha: Sahil Arora, so why there is no glitch in Qp

- username: +Sonnix Jackson But you r changing the signal (glitches) when the clock signal is high in both, Qm and Qp, so why the glitches do not affect Qp

- Sonnix Jackson: +pranav satbhai Rewatch the video - this has been explained clearly ;)

- yusuf berat gedikoğlu: I think, there is no arrow sign with clock input on device. It was edge triggered when there is arrow on the device. On the other hand it was level triggered. :)

- Rohit Sudhakar: awesome explanation! thanks a lot

- MB Design: Hi! I`m asking myself the same question at this moment. Have you found out if it does or not? THX

- Abdullah Naeem: u said in previous lecture that u r using Master Slave Flip Flop to overcome the problem of 1 ,1 condition as in JK and racing Condition, but now u r using D flip Flop which can't take 1 , 1 as input. Why??

- Ph. Vedant Sharma: I have a confusion between Qm and Qp. Both are D FFs but they produce different waveforms that is the first one is level triggered while the second one is edge triggered. Anyways great video.

- Yacoub Oulad Daoud: Very helpful!

- Naresh Kumar: Excellent!

- Madhu Kashyap: Are master slave JK flip flop and master slave D flip flop same?

- Utkarsh ahuja: Sir which software do you use for making these lectures and on which desktop/pad ?

- Henrique Baqueiro: Outstanding video, but what about the positive edge flip-flops, how to build them?

- Sonnix Jackson: +nmerinos In edge triggered the signal state is taken on the edge, no changes are taking place in those instances. You need to look at the output on the edges - what is in between the edges is the stored value captured at the edges, hence no glitches.

- Yashveer singh Yadav: In this example, you have not taken that case in which 'D' and clock is changing together

- Nazish Khalid: how to make positive edge d flip flop

- Vari Veera: Yeah I was wondering that as well. Aren't all Flipflops edge triggered? And in a previous video you mentioned that Master-Slave Operation is negative edge triggering. Please clarify, thanks.

- Asif AsEE: perfect

- tyja: +Henrique Baqueiro it is just the D block with the clock but recognizing that Q only takes on the value of D at positive edge trigger

- srinadh j: He said master slave as negative edge triggering but it does not use negative edge triggering,it uses level triggering . it just behaves as negative edge triggering as we can see at the end both the diagrams of master slave and negative edge triggering are same .

- Burak İbrahim Ünal: Finally understood.Thanks...

- Sonnix Jackson: Fantastic - so many concepts in a short video. Thank you.

- diivya k.s: while drawing Qm,why isn,t retaining the previous value of D but instead it Qm is following exact changes in D ?

- Surya Teja: Ans to why Qp and Qm does not give the same o/p. Here D flip flop is a line triggering flip flop so the o/p changes to a certain level of the clock pulse,we will get Qm according to the i/p that is D,but where as Qp is a edge triggering flip flop.

- PaddythePackman: Nice Video but its a pity, that your accent is pretty strong. Anyways thanks for the help. =)

- Nitesh Singh: nice video

- Neso Academy: +David Pham Welcome!!

- Neso Academy: Please follow the playlist of digital electronics (https://www.youtube.com/playlist?list=PLBlnK6fEyqRjMH3mWf6kwqiTbT798eAOm)

- Giovanni Giannone: You say that I can use Master Slave FF or Neg. Edge trigg. FF to overcome glitches. But if I have not desired signals near negative edge triggering, can I use configuration of Neg. Edge trigg. FF anyway?

- pranav satbhai: in positive and negative edge triggering we are following the d input, then why does glitches do not occur in positive and negative edge triggering?

- Χρήστος Στέφο: Therefore d,jk,sr-flip flops are actually latches? And only master slave d an master slave jk are flip-flops? That's what i could understand throught this presentation. https://www.youtube.com/watch?v=m1QBxTeVaNs&index=143&list=PLBlnK6fEyqRjMH3mWf6kwqiTbT798eAOm

- khwaja wisal: i think sir your waveform for Qp is wrong because when second clock pilse is still high d changes from 0 to 1 and you didnt consider that change

- shubham sinha: why we have considered glitch in Qm and not in QP? Please reply this question?

- Ravi Ranjan: yes, glitches will happen to remove

- Saurav Likhar: what will be output waveform in case of Qp and Qn when D signal will change at the same time clock changes.

- Suhad Hadad: Many thank for the good explanation

Behaviour of Master Slave D Flip Flop | |

| 242,726 views views | 468,989 followers |

| 1,099 Likes | 1,099 Dislikes |

| Education | Upload TimePublished on 21 Mar 2015 |

Không có nhận xét nào:

Đăng nhận xét